高科技企业开发复杂的芯片,封装和单板努力克服由于飞速增长的IC速度和数据传输速率联合引起的供电电压的降低,更高密度,越来越小型化的结构引起的电源完整性和信号完整性问题。同时,更高的I/O数目,多堆叠的芯片和封装以及更高的电气性能约束都使得IC封装物理设计更加复杂。

Cadence具有突破型进展的解决方案,基于Sigrity专利技术,解决这些设计挑战。该解决方案致力于完整的电源供电系统分析跨越了芯片,封装和单板;系统级的信号完整性(SI)分析,包含高速信号传输同步反转噪声和单个和多个芯片封装,最先进的 3D封装以及系统级封装(SiPs)的高级物理设计。

Power Integrity电源完整性

Cadence

电源完整性(PI)解决方案,基于Sigrity技术,提供signoff级别精度的PCB和IC封装的AC和DC电源分析。每个工具都能与Cadence Allegro® PCB 和IC封装物理设计解决方案无缝集成。

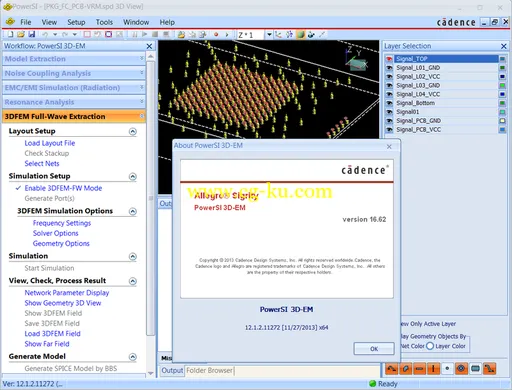

Sigrity PowerSI

IC封装和PCB设计快速准确的全波电磁场分析

作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。

Sigrity™ PowerSI®可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压超标等问题,从而帮助用户发现或改善潜在的设计风险。

PowerSI可以方便的提取封装和PCB的各种网络参数(S/Y/Z),并对复杂的空间电磁谐振问题产生可视化的输出。PowerSI能与当前主流的物理设计数据库如PCB, IC封装和系统级封装(SiP)进行无缝连接。

主要功能

• 为IC封装和PCB的电源分配网络(PDN)的可靠设计提供指导

• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据

• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型

• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据

• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据

• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响

• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取

• 与三维(3D)IC封装设计和板级设计工具无缝集成

优势与特点

• 专业的频域分析工具,致力于Package/PCB全面的信号完整性、电源完整性、EMI/EMC的分析,有10年的历史,经过数以千计的设计产品验证,成熟可靠

• 算法稳定可靠,即使对不规则的平面结构也能精确求解

• 提供智能的多CPU、多任务分布式计算能力,可以把一个大型的复杂任务分配给多个CPU或多台计算机同步完成,从而大大提高了仿真效率。

• 独特高效的电磁场分析技术使得PowerSI对多层电源地平面、大量的过孔和走线等复杂和规模巨大的封装和PCB设计依然能快速有效求解;

• 具有灵活多样的2D和3D fly-through等显示方式• 支持各种灵活的端口定义选项,允许用户自定义基于节点、器件、管脚、网络等方式产生端口

• 强大的SPICE语法支持能力

• 与各种ECAD数据库如Cadence® SiP Layout, Allegro® Package Designer, 和 Allegro PCB Designer ,以及Mentor, Zuken和Altium设计都有专门优化的接口

Cadence

Allegro Sigrity

16.62 | 2.8 Gb

Cadence Design Systems, Inc. released an updated version Cadence Sigrity 6.62, with technologies provide the signal integrity and power analysis solutions needed for system-level verification and interface compliance.

Increases in IC speed, faster data transmission rates, smaller geometries, and an emphasis on optimization have made power and signal integrity issues tightly connected. To address these issues, designers need advanced power integrity and power-aware signal integrity tools. This level of technology allows designers to see the complete picture and achieve signoff-level verification through their analysis. Mistakes are not an option on projects this advanced, that's why designers choose proven Sigrity solutions, from Cadence.

By adopting Sigrity solutions, designers can perform three major tasks of the design verification process:

- Analyze the complete power delivery system across chips, packages, and boards.

- Perform system-level signal integrity (SI) analysis, including simultaneous switching noise analysis of high-speed signal transmissions.

- Utilize the advanced physical design tools for single and multi-chip packages, state-of-the-art 3D packages, and systems-in-package (SiPs).

What’s New in 16.62

ASIS 16.62 introduces three new products to the Allegro Sigrity Product Line:

- Allegro Sigrity PI Base

The Allegro Sigrity PI Base is a complement to the Allegro Sigrity SI Base (PA5700) in that it utilizes the Allegro canvas for viewing and casual editing of Allegro PCB, Package, or SiP files. PI Base provides first order Power Integrity checks to be performed. The tool is meant to be used either by designers who need to seek guidance during the layout process, or by Power Integrity experts, who need a quick answer, and understand the confidence level that can be applied with the first-order analysis.

- Allegro Sigrity Signoff and Optimization Option

The Allegro Sigrity Power Integrity Signoff and Optimization Option integrates with PI Base to provide expert-level power integrity analysis on top of an editing canvas that allows for the design to be changed and reanalyzed in an integrated fashion. This Option includes the ability to run all of these Sigrity tools (one at a time) either directly from the PI Base (PA5800) or as a point tool: PowerDC, OptimizePI, PowerSI, 3D-EM, CAD Translators

- IO-SSO Analysis Suite

The IO-SSO Analysis Suite is a specific group of model creation and analysis tools that provides the ability to accurately simulate a group of parallel bus nets that are switching simultaneously. For example, a DDR3 data bus could have as many as 64 simultaneous switching signals. The noise on the power and ground planes, known as simultaneous switching noise (SSN), must be accurately characterized to understand if the data will always be reliable. This suite of tools provides all the functionality required for modeling chip, package, and PCB from die to die. The simulation tool provided understands modern memory interface protocols (such as DDR3/DDR4) and points out violations to the electrical specification for those standard protocols. This Suite includes the ability to run all of these Sigrity tools (one at a time) as a point tool: T2B, XcitePI Extraction, XtractIM, PowerSI, Broadband SPICE, SystemSI – PBA, CAD Translators

About Cadence Design Systems, Inc.

Cadence enables global electronic design innovation and plays an essential role in the creation of today's integrated circuits and electronics. Customers use Cadence software, hardware, IP, and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers, and research facilities around the world to serve the global electronics industry.

About Sigrity

Sigrity develops and globally supports advanced software analysis solutions to ensure power integrity and signal integrity in chips, packages and printed circuit boards; and physical design tools for single die and SiP implementations. Over 250 companies utilize Sigrity products as part of industry standard design flows and with layout tools from Cadence, Mentor Graphics, Zuken and other EDA suppliers. Sigrity solutions help companies overcome design challenges to reduce costly respins and get to market faster.

Over 60% of Sigrity's 100+ employees are in research and development positions creating breakthrough solutions targeting real-world challenges.

Name:

Cadence Allegro Sigrity

Version:

16.62.002

Home:

www.cadence.com

Interface:

english

OS:

Windows Seven / 8

System Requirements:

Preinstall Cadence SPB 16.60.016 or above

Size:

2.8 Gb

Download k2s

http://k2s.cc/file/52db22a838746/nceCllSi1662.part1.rar

http://k2s.cc/file/52db22a34d84c/nceCllSi1662.part2.rar

http://k2s.cc/file/52db221d3853a/nceCllSi1662.part3.rar

发布日期: 2014-01-19