当使用大型FPGA上确保FPGA的引脚连接到正确的信号PCB的是一个繁重的任务。FPGA侧的引脚分配形式在FPGA上实现的逻辑顶层的HDL信号。PCB上侧引脚连接到正确的网,将连接在PCB上其他元件。由于FPGA和PCB的实施往往是并行完成,所使用的信号名称并不总是相同。为了使事情更糟糕的,它往往是要执行针掉期,以防止PCB布线问题。这些引脚互换FPGA和PCB。由于这是几乎总是体力劳动,和当前的设备已超过1500针,一个错误是很容易的。

Verifing一个FPGA在6分钟内

验证的FPGA

智能验证在6分钟内

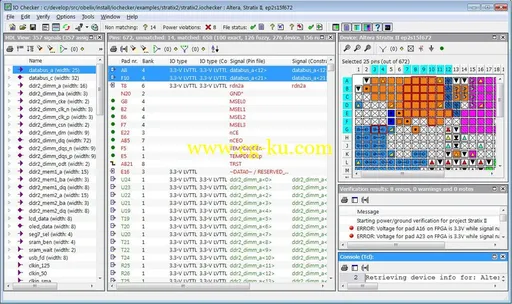

IO检查使用规则(基于正则表达式)在FPGA和PCB设计环境相匹配的信号名称。它允许工具来验证匹配的群体虽然单个信号仍然可以有所不同。这些规则可以自动生成由设计师微调。自动化的方法往往会匹配所有器件引脚的80%至90%。

检查的IO的灵活性,允许它在任何设计流程中使用,不需要任何的设计方法。在与排序的问题的看法相结合的规则发生器,使工程师能够验证在半小时内1000 +引脚设备。

一旦该项目及其规则的定义,它是一个简单的任务,以保持FPGA和PCB数据的一致性。所有过时的文件是在一个动作处理,并报告所有的改变都。

在6分钟内创建的约束

创建约束

在6分钟内

IO检查概述

特点和优点

比较FPGA和PCB的引脚名使用正则表达式

创建和更新FPGA约束文件

自动规则生成363

电源引脚的电压检查

用户指示接受验证差异

单击验证和一致性

报告增量的变化,在引脚和净列表

集中在十几差异,而不是千行

适用于任何设计流程

HTML报告

HDL Works IO Checker 3.x (Win/Lnx) | 49/48 MB

When using large FPGA's on a PCB making sure that the FPGA pins are connected to the right signals is a cumbersome task. On the FPGA side the pins are assigned to the HDL signals that form the toplevel of the logic implemented on the FPGA. On the PCB side the pins have to be connected to the proper net that will connect it to other components on the PCB. Because implementation of FPGA and PCB is often done in parallel, the signal names used are not always identical. To make things even worse, it is often necessary to perform pin swaps to prevent PCB routing problems. These pin swaps have to be made both on the FPGA and the PCB. As this is almost always manual work, and current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification

IO Checker uses rules (based on regular expressions) to match the signal names in both the FPGA and PCB design environment. It allows the tool to validate groups of matches although individual signals can still differ. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pins device in half an hour.

Once the project and its rules are defined it is a simple task to keep the FPGA and PCB data consistent. All out-of-date files are processed in one action and all changes are reported.

Features & Benefits

- Compare FPGA and PCB pin names using regular expressions

- Create & update FPGA constraint file

- Automatic rule generation

- Voltage checks for power pins

- User directed acceptance of verified differences

- One click verification and consistency

- Reports incremental changes in pin- and net list

- Concentrate on a dozen differences instead of a thousand lines

- Fits in any design flow

- HTML report

Home Page

-

http://www.hdlworks.com/products/iochecker/index.html

发布日期: 2016-03-16