Learn VHDL and FPGA Development with a BASYS 3

MP4 | Video: AVC 1280x720 | Audio: AAC 44KHz 2ch | Duration: 13.5 Hours | 1.63 GB

Genre: eLearning | Language: English

Learn how to create a VHDL design that can be simulated and implemented on an FPGA development board.

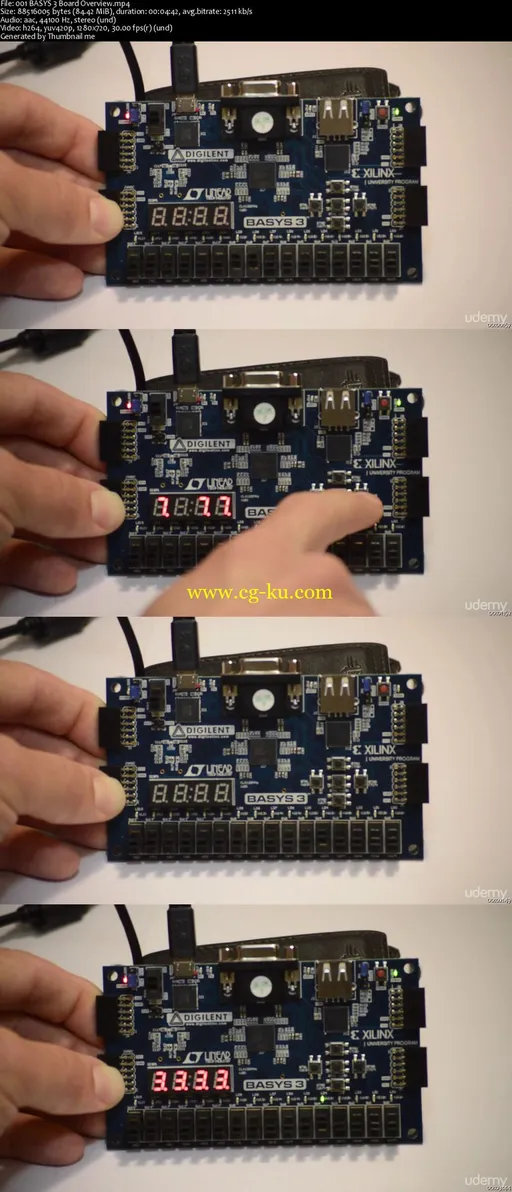

VHDL and FPGA Development for Beginners and Intermediates is a course that is designed to teach students how to create and successfully simulate their VHDL design. We will also be implementing these designs on a Xilinx BASYS 3 or BASYS 2 FPGA development board so that the students can see their designs actually running. This course starts from beginning to end in teaching the user how to turn their digital logic design into VHDL designs that can be simulated in ModelSim or ISim and then implemented on an FPGA development board. This course also covers how to use Altera's tools so students are not limited to Xilinx development boards.

Course Structure:

This course contains over 20 lectures that will teach students the syntax and structure of VHDL. The student will be able to understand the syntax and use of specific VHDL keywords by taking this course. There are lectures included in each lab to give a background on the digital logic circuit the student will be implementing.

This course contains 7 labs that are designed so that the student will learn how to develop VHDL code. For each lab I will give the student a set of VHDL files that they will have to modify or change in order to get the project to simulate correctly in ModelSim and so they can implement the design on their FPGA board. These labs are design to help the students learn VHDL by actually coding it themselves.

Please message me before you sign up for this course!

发布日期: 2016-02-21